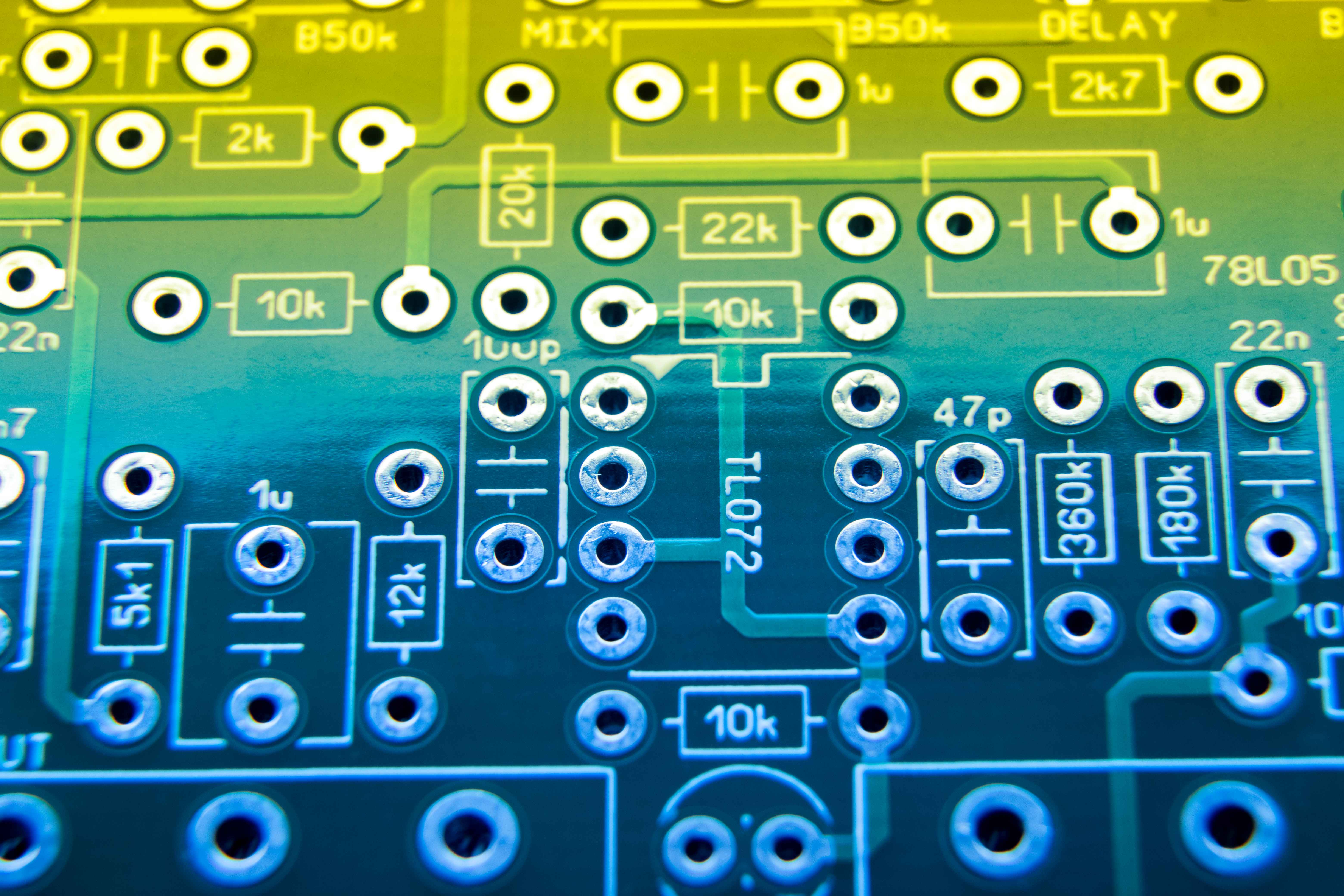

Testability Analysis: During the early stages of chip design, testability analysis is performed to identify potential testability issues and to determine the best DFT techniques suitable for the specific design. This analysis helps in making informed decisions about the testability requirements of the chip.

One of the most widely used DFT techniques is the insertion of scan chains. Scan chains are shift registers that allow the conversion of sequential elements into a single large shift register. By doing so, it becomes easier to apply test patterns and observe responses during testing, significantly improving testability.

Test data volume can become challenging as chip complexity increases. Test compression techniques help in reducing the volume of test data required to test the chip without compromising fault coverage. This enables efficient use of test resources and reduces test time.

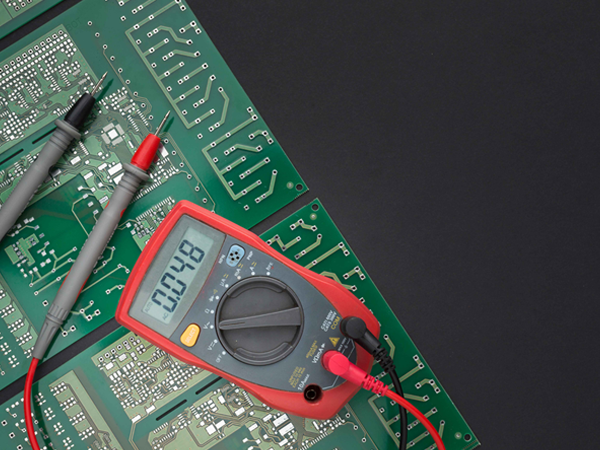

Joint Test Action Group (JTAG) or boundary scan is a technique that enables testing of interconnections and boundary values of chip I/Os. It facilitates access to internal signals and simplifies the testing of chips on the PCB level.

Memory BIST is used to test embedded memories within the chip. Dedicated test circuits are used to apply test patterns and analyze the responses from the memory blocks, ensuring their reliability.

ATPG tools automatically generate test patterns that can detect specific faults in the design. These patterns are aimed at maximizing fault coverage while minimizing test time.

Various fault models are used to represent different types of manufacturing defects and faults that might occur in the chip. These models help in evaluating the effectiveness of the test patterns and DFT techniques.

For complex designs, hierarchical DFT is employed, where DFT structures are organized in a hierarchical manner to facilitate efficient testing and ease of debugging.